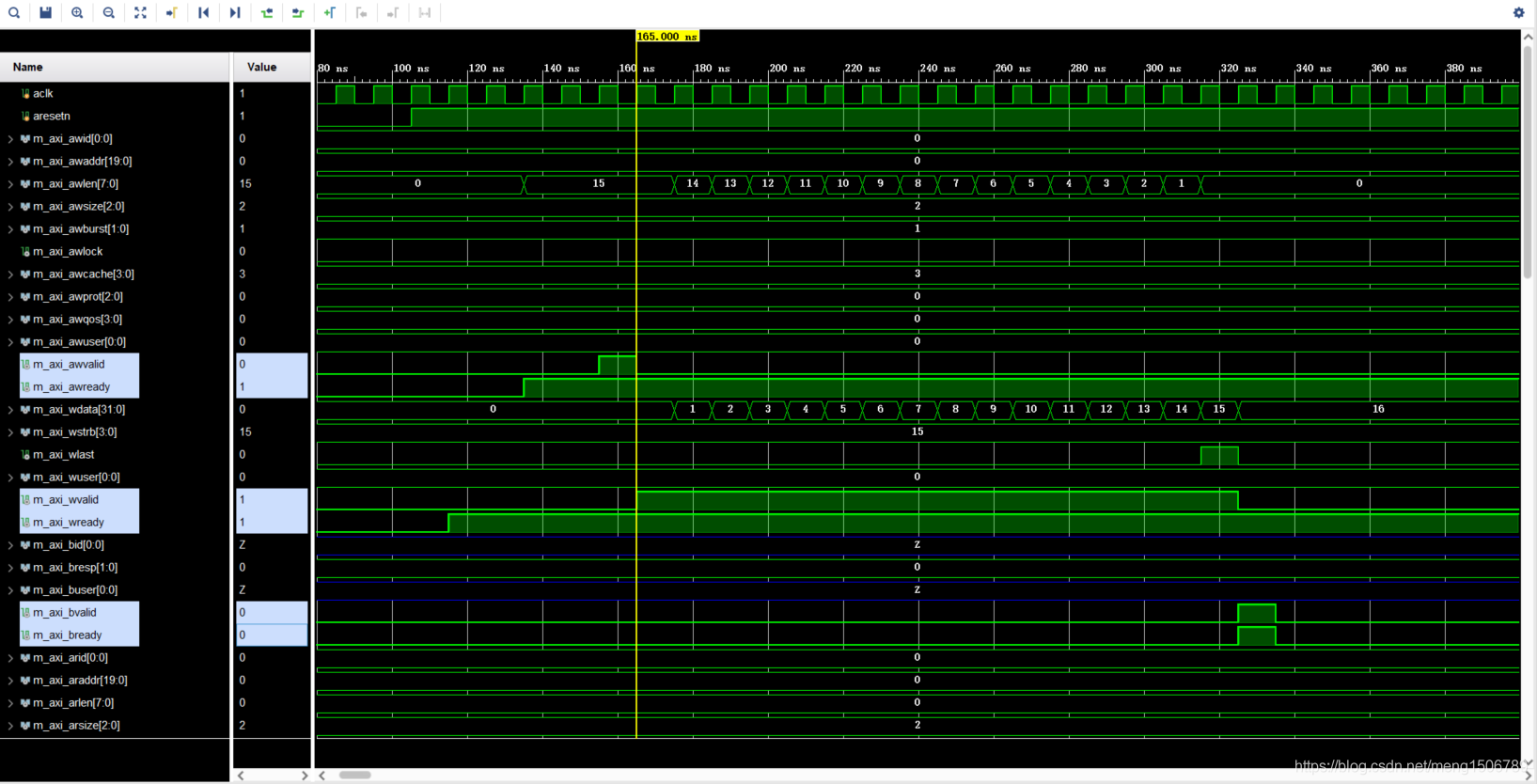

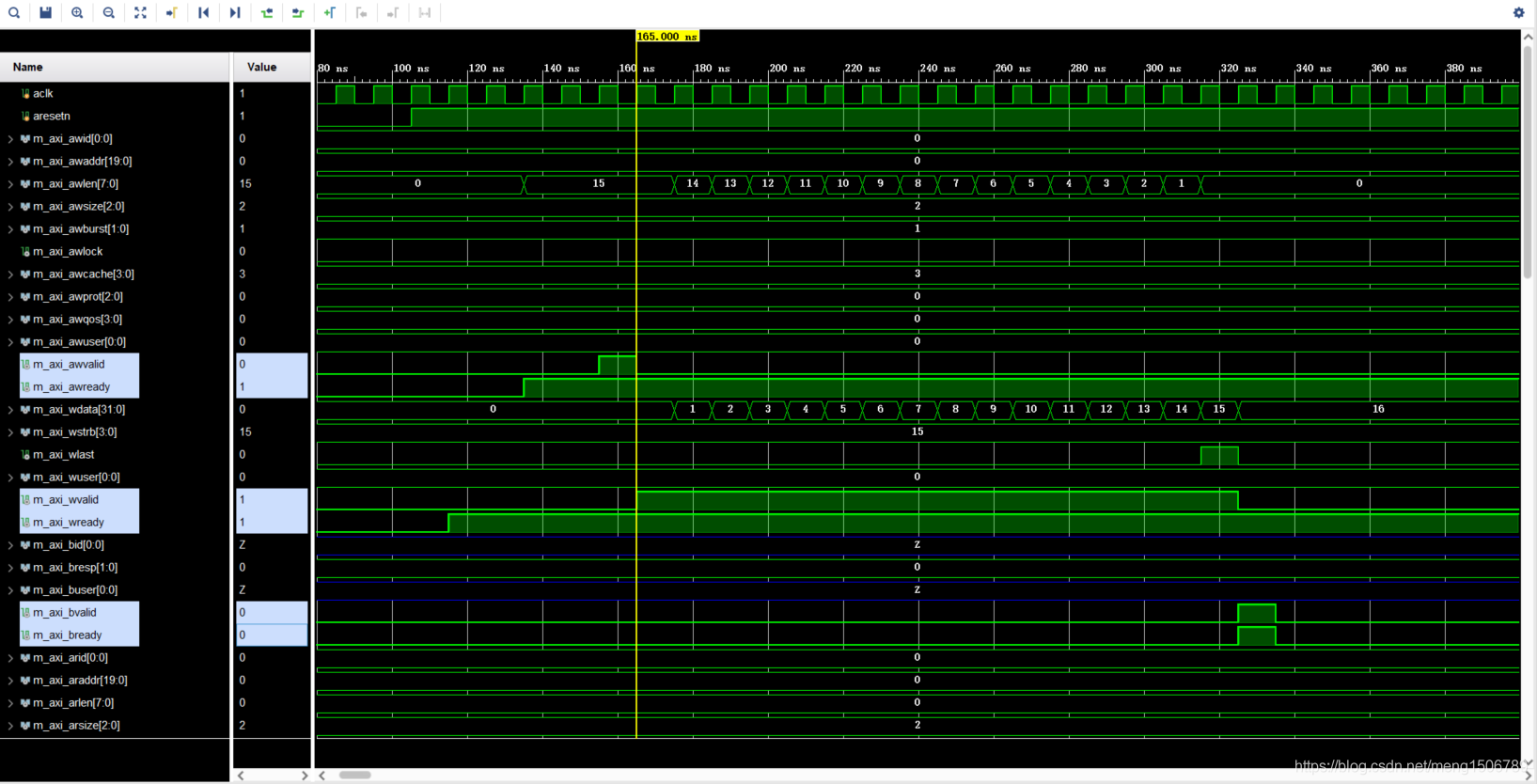

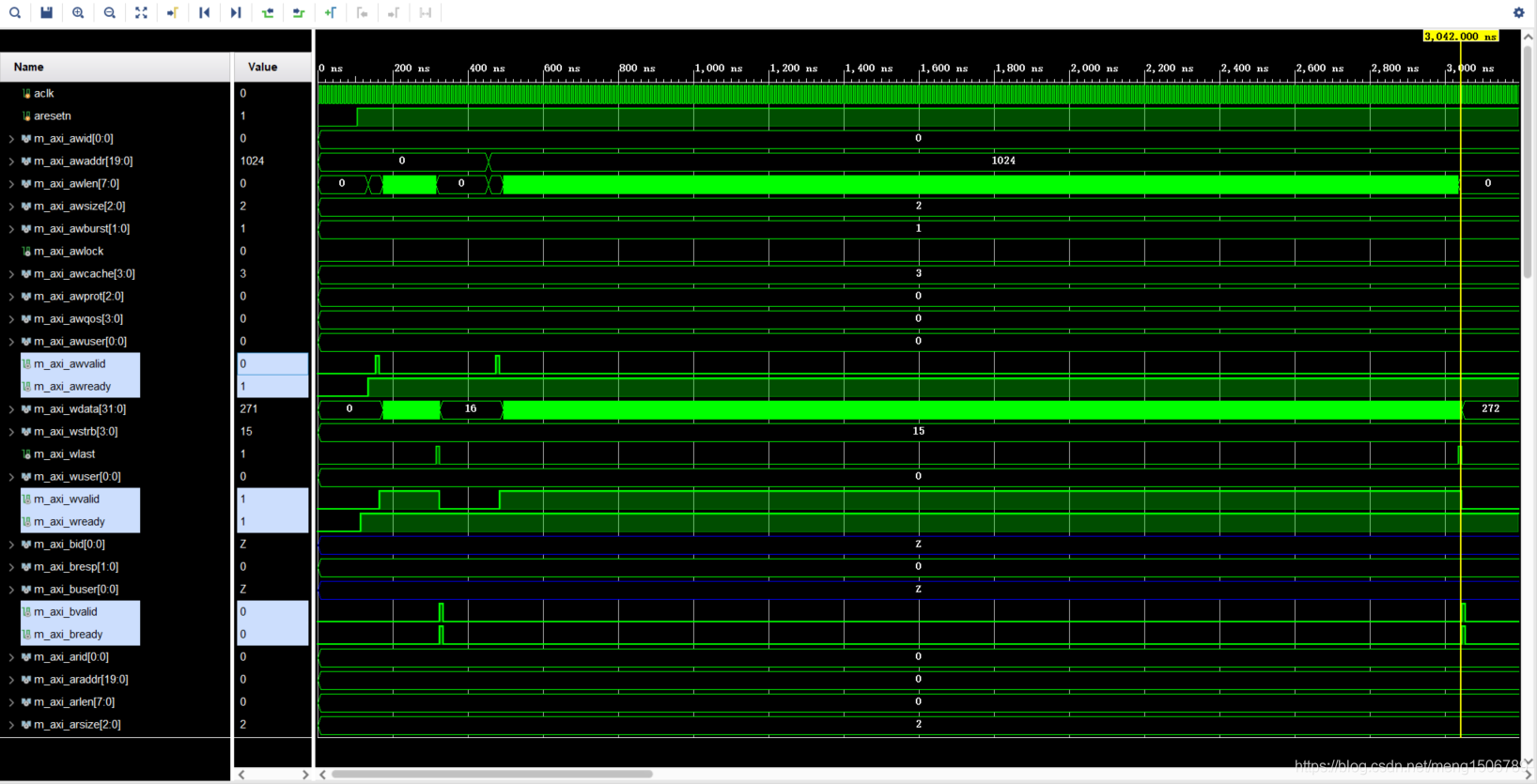

预览截图

应用介绍

AXI(Advanced eXtensible Interface)总线是AMBA总线架构中,最新并且性能最好的一个总线标准。AXI的设计目标是可以在高时钟频率下运行,并在延滞时间长的状况下仍可达成高数据吞吐率。AXI总线将读/写请求与读/写结果相互分离、将数据写入和数据读出的信号相分离,可以同时进行写入和读出动作,从而最大限度地提高总线的数据吞吐率。

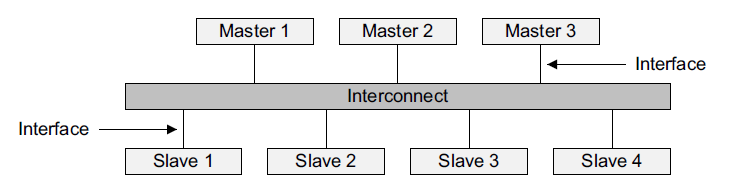

由若干master设备和slave设备通过一些形式的interconnect组成的典型的系统如下图所示,AXI总线即可作为其中的Interface,实现数据通信。

amba_axi_protocol_spec的下载地址:

https://static.docs.arm.com/ihi0022/g/IHI0022G_amba_axi_protocol_spec.pdf?_ga=2.83582867.447931395.1591251023-1939436544.1591251023

时钟与复位

Clock

每个AXI interface都有一个时钟信号ACLK,所有的输入信号在ACLK的上升沿采样,所有的输出信号在ACLK的上升沿之后发生变化。

在master和slave interface上,输入与输出信号之间必须没有组合逻辑路径。

Reset

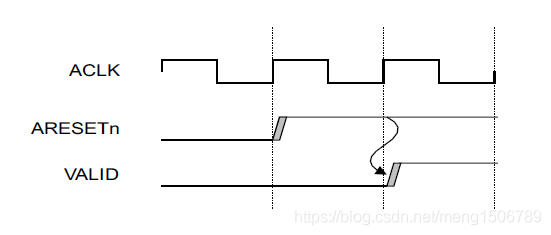

AXI协议使用低电平有效的复位信号ARESETn。复位信号可以被异步置位,但是复位的释放必须与ACLK的上升沿是同步的。

During reset,需要遵循下面的interface requirement:

(1)A master interface must drive ARVALID, AWVALID, and WVALID LOW.

(2)A slave interface must drive RVALID and BVALID LOW.

(3)All other signals can be driven to any value.

在复位之后,master被允许驱动ARVALID, AWVALID, or WVALID 为高电平的最早的时刻是ARESETn为高电平之后的一个ACLK的上升沿,如下图所示。

AXI的5个通道

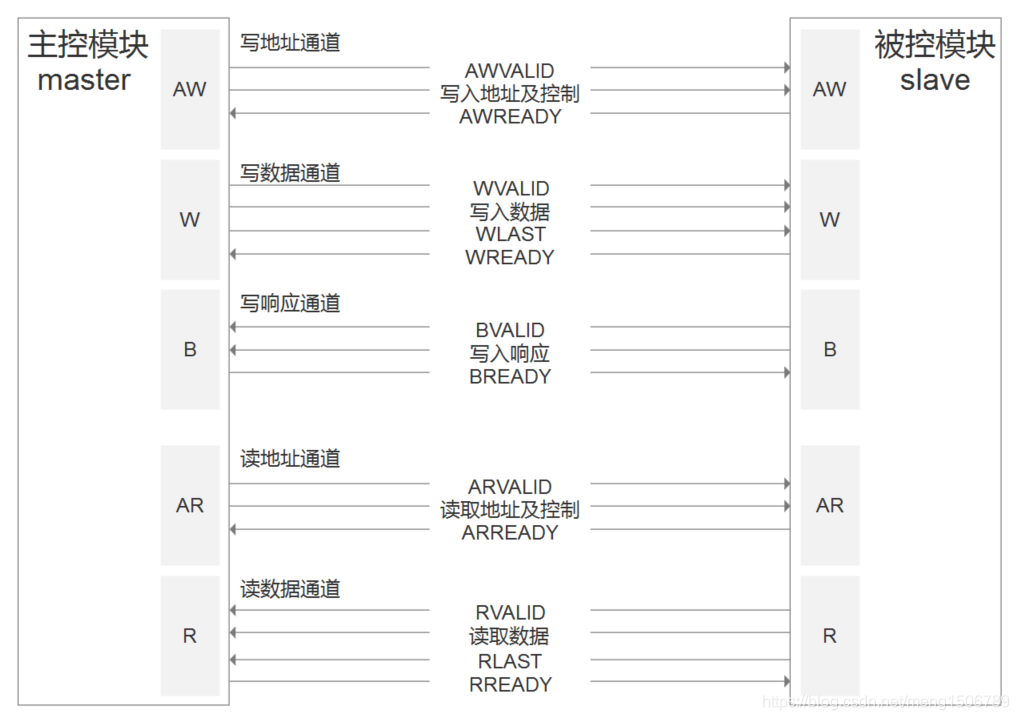

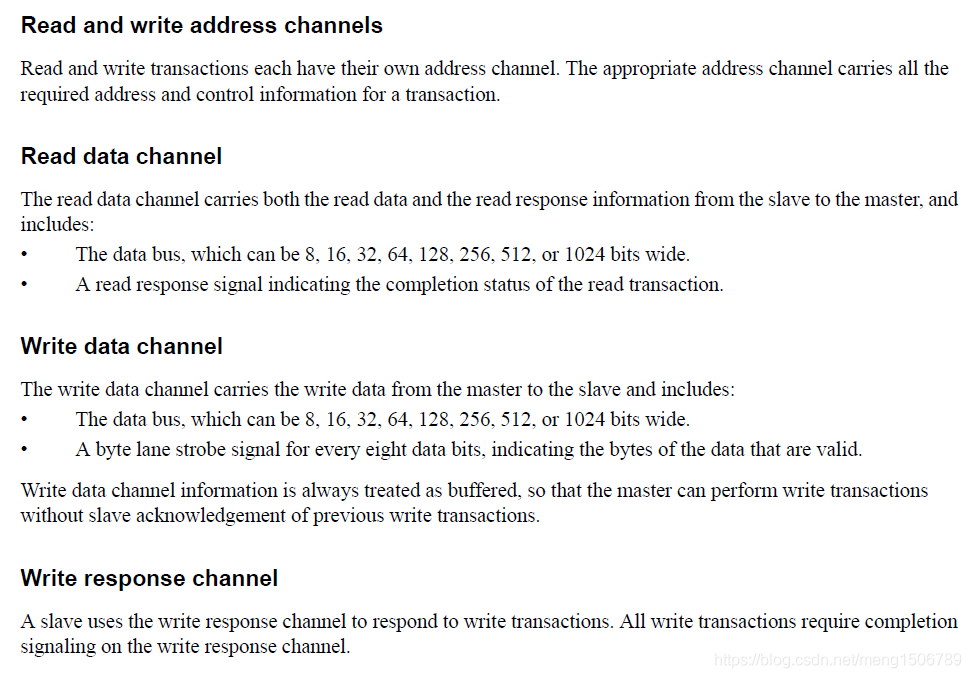

AXI总线的master和slave的端口分为5个双向流量控制的通道,如下图所示。所谓双向流量控制是指发送端用valid表示数据是有效的,接收端用ready表示可以接受数据;只有在vaild和ready同时为1时,数据才成功被传送。vaild/ready机制可以使发送接收双方都有能力控制传输速率。

AXI规定:

(1)A source is not permitted to wait until READY is asserted before asserting VALID .

(2)When VALID is asserted, it must remain asserted until the handshake occurs.

©版权声明:本文内容由互联网用户自发贡献,版权归原创作者所有,本站不拥有所有权,也不承担相关法律责任。如果您发现本站中有涉嫌抄袭的内容,欢迎发送邮件至: www_apollocode_net@163.com 进行举报,并提供相关证据,一经查实,本站将立刻删除涉嫌侵权内容。

转载请注明出处: apollocode » ZYNQ7020 AXI 总线仿真

文件列表(部分)

| 名称 | 大小 | 修改日期 |

|---|---|---|

| 095bcbcb4d8045e3.xci | 0.83 KB | 2022-03-10 |

| maxi_full_v1_0_bfm_1_maxi_full_0_0.dcp | 62.34 KB | 2022-03-10 |

| maxi_full_v1_0_bfm_1_maxi_full_0_0_sim_netlist.v | 8.80 KB | 2022-03-10 |

| maxi_full_v1_0_bfm_1_maxi_full_0_0_sim_netlist.vhdl | 8.91 KB | 2022-03-10 |

| maxi_full_v1_0_bfm_1_maxi_full_0_0_stub.v | 1.16 KB | 2022-03-10 |

| maxi_full_v1_0_bfm_1_maxi_full_0_0_stub.vhdl | 1.02 KB | 2022-03-10 |

| 5bfe11094a702d58.xci | 0.83 KB | 2021-11-05 |

| maxi_full_v1_0_bfm_1_maxi_full_0_0.dcp | 62.40 KB | 2021-11-05 |

| maxi_full_v1_0_bfm_1_maxi_full_0_0_sim_netlist.v | 8.80 KB | 2021-11-05 |

| maxi_full_v1_0_bfm_1_maxi_full_0_0_sim_netlist.vhdl | 8.91 KB | 2021-11-05 |

| maxi_full_v1_0_bfm_1_maxi_full_0_0_stub.v | 1.16 KB | 2021-11-05 |

| maxi_full_v1_0_bfm_1_maxi_full_0_0_stub.vhdl | 1.02 KB | 2021-11-05 |

| 7279c1db3c00f9af.xci | 0.97 KB | 2021-11-05 |

| maxi_full_v1_0_bfm_1_slave_0_0.dcp | 12.54 KB | 2021-11-05 |

| maxi_full_v1_0_bfm_1_slave_0_0_sim_netlist.v | 2.12 KB | 2021-11-05 |

| maxi_full_v1_0_bfm_1_slave_0_0_sim_netlist.vhdl | 1.87 KB | 2021-11-05 |

| maxi_full_v1_0_bfm_1_slave_0_0_stub.v | 1.09 KB | 2021-11-05 |

| maxi_full_v1_0_bfm_1_slave_0_0_stub.vhdl | 0.98 KB | 2021-11-05 |

| cc296d04268a0a65.xci | 0.97 KB | 2022-03-10 |

| maxi_full_v1_0_bfm_1_slave_0_0.dcp | 12.48 KB | 2022-03-10 |

| maxi_full_v1_0_bfm_1_slave_0_0_sim_netlist.v | 2.11 KB | 2022-03-10 |

| maxi_full_v1_0_bfm_1_slave_0_0_sim_netlist.vhdl | 1.87 KB | 2022-03-10 |

| maxi_full_v1_0_bfm_1_slave_0_0_stub.v | 1.09 KB | 2022-03-10 |

| maxi_full_v1_0_bfm_1_slave_0_0_stub.vhdl | 0.98 KB | 2022-03-10 |

| ssm.db | 0.25 KB | 2021-11-05 |

| gui_handlers.wdf | 0.85 KB | 2022-03-10 |

| java_command_handlers.wdf | 0.24 KB | 2022-03-10 |

| project.wpc | 0.06 KB | 2022-03-10 |

| synthesis.wdf | 0.72 KB | 2022-03-10 |

| webtalk_pa.xml | 1.42 KB | 2022-03-10 |

发表评论 取消回复