带测试平台的计数器的VHDL代码

此项目是带测试平台的计数器VHDL代码。在此VHDL项目中,计数器在VHDL中实现。 计数器的测试台VHDL代码也与仿真波形一起显示。附件中包括:递增计数器的VHDL代码、递增计数器的Testbench VHDL代码、减计数器的VHDL代码、递减计数器的Testbench VHDL代码、上下计数器的VHDL代码、向下计数器的Testbench VHDL代码等等。了解更多请下载附件。

应用介绍

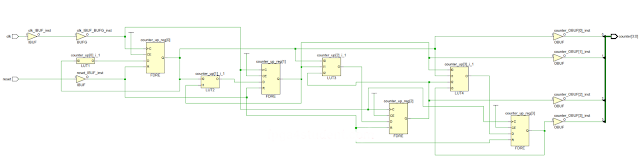

此项目是带测试平台的计数器VHDL代码。

在此VHDL项目中,计数器在VHDL中实现。 计数器的测试台VHDL代码也与仿真波形一起显示。

附件中包括:递增计数器的VHDL代码、递增计数器的Testbench VHDL代码、减计数器的VHDL代码、递减计数器的Testbench VHDL代码、上下计数器的VHDL代码、向下计数器的Testbench VHDL代码;另外还有递增计数器仿真波形、递减计数器仿真波形、向下计数器仿真波形。

本人在下方展示了递增计数器的VHDL代码;想了解更多请下载附件。

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

-- FPGA projects using Verilog code VHDL code

-- fpga4student.com: FPGA projects, Verilog projects, VHDL projects

-- VHDL project: VHDL code for counters with testbench

-- VHDL project: VHDL code for up counter

entity UP_COUNTER is

Port ( clk: in std_logic; -- clock input

reset: in std_logic; -- reset input

counter: out std_logic_vector(3 downto 0) -- output 4-bit counter

);

end UP_COUNTER;

architecture Behavioral of UP_COUNTER is

signal counter_up: std_logic_vector(3 downto 0);

begin

-- up counter

process(clk,reset)

begin

if(rising_edge(clk)) then

if(reset='1') then

counter_up <= x"0";

else

counter_up <= counter_up + x"1";

end if;

end if;

end process;

counter <= counter_up;

end Behavioral;

©版权声明:本文内容由互联网用户自发贡献,版权归原创作者所有,本站不拥有所有权,也不承担相关法律责任。如果您发现本站中有涉嫌抄袭的内容,欢迎发送邮件至: www_apollocode_net@163.com 进行举报,并提供相关证据,一经查实,本站将立刻删除涉嫌侵权内容。

转载请注明出处: apollocode » 带测试平台的计数器的VHDL代码

文件列表(部分)

| 名称 | 大小 | 修改日期 |

|---|---|---|

| 带测试平台计数器的VHDL代码 (附件).txt | 0.93 KB | 2020-04-05 |

| counter.png | 21.67 KB | 2020-04-05 |

| counter1.png | 51.65 KB | 2020-04-05 |

| counter2.png | 60.83 KB | 2020-04-05 |

| counter3.png | 43.18 KB | 2020-04-05 |

| image | 0.00 KB | 2020-04-05 |

发表评论 取消回复