停车场系统的Verilog代码

此项目是停车场系统的Verilog代码。这个简单的项目是在Verilog中实现停车场系统。 停车场系统的Verilog代码已完整显示。在停车系统的入口处,有一个传感器被激活以检测车辆驶来。 触发传感器后,需要输入密码才能打开门。 如果输入的密码正确,则门将打开以允许车辆进入。否则,门仍被锁定。 如果当前汽车正驶入停车场,并被出口传感器检测到而另一辆汽车驶入,则门将被锁定,并要求即将驶来的汽车输入密码。

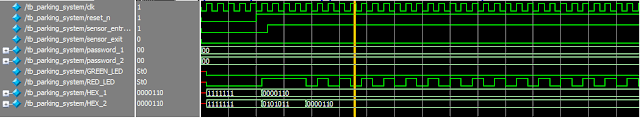

预览截图

应用介绍

此项目是停车场系统的Verilog代码。这个简单的项目是在Verilog中实现停车场系统。 停车场系统的Verilog代码已完整显示。在停车系统的入口处,有一个传感器被激活以检测车辆驶来。 触发传感器后,需要输入密码才能打开门。 如果输入的密码正确,则门将打开以允许车辆进入。否则,门仍被锁定。 如果当前汽车正驶入停车场,并被出口传感器检测到而另一辆汽车驶入,则门将被锁定,并要求即将驶来的汽车输入密码。附件得文件中包括:停车场系统的Verilog代码、用于停车系统的Testbench Verilog代码、Verilog中的停车场系统的仿真波形。本人在预览区展示了Verilog中的停车场系统的仿真波形;在下方展示了停车场系统的Verilog代码;如想了解得更多请下载附件。

// fpga4student.com FPGA projects, Verilog projects, VHDL projects

// Verilog project: Verilog code for car parking system

`timescale 1ns / 1ps

module parking_system(

input clk,reset_n,

input sensor_entrance, sensor_exit,

input [1:0] password_1, password_2,

output wire GREEN_LED,RED_LED,

output reg [6:0] HEX_1, HEX_2

);

parameter IDLE = 3'b000, WAIT_PASSWORD = 3'b001, WRONG_PASS = 3'b010, RIGHT_PASS = 3'b011,STOP = 3'b100;

// Moore FSM : output just depends on the current state

reg[2:0] current_state, next_state;

reg[31:0] counter_wait;

reg red_tmp,green_tmp;

// Next state

always @(posedge clk or negedge reset_n)

begin

if(~reset_n)

current_state = IDLE;

else

current_state = next_state;

end

// counter_wait

always @(posedge clk or negedge reset_n)

begin

if(~reset_n)

counter_wait <= 0;

else if(current_state==WAIT_PASSWORD)

counter_wait <= counter_wait + 1;

else

counter_wait <= 0;

end

// change state

// fpga4student.com FPGA projects, Verilog projects, VHDL projects

always @(*)

begin

case(current_state)

IDLE: begin

if(sensor_entrance == 1)

next_state = WAIT_PASSWORD;

else

next_state = IDLE;

end

WAIT_PASSWORD: begin

if(counter_wait <= 3)

next_state = WAIT_PASSWORD;

else

begin

if((password_1==2'b01)&&(password_2==2'b10))

next_state = RIGHT_PASS;

else

next_state = WRONG_PASS;

end

end

WRONG_PASS: begin

if((password_1==2'b01)&&(password_2==2'b10))

next_state = RIGHT_PASS;

else

next_state = WRONG_PASS;

end

RIGHT_PASS: begin

if(sensor_entrance==1 && sensor_exit == 1)

next_state = STOP;

else if(sensor_exit == 1)

next_state = IDLE;

else

next_state = RIGHT_PASS;

end

STOP: begin

if((password_1==2'b01)&&(password_2==2'b10))

next_state = RIGHT_PASS;

else

next_state = STOP;

end

default: next_state = IDLE;

endcase

end

// LEDs and output, change the period of blinking LEDs here

always @(posedge clk) begin

case(current_state)

IDLE: begin

green_tmp = 1'b0;

red_tmp = 1'b0;

HEX_1 = 7'b1111111; // off

HEX_2 = 7'b1111111; // off

end

WAIT_PASSWORD: begin

green_tmp = 1'b0;

red_tmp = 1'b1;

HEX_1 = 7'b000_0110; // E

HEX_2 = 7'b010_1011; // n

end

WRONG_PASS: begin

green_tmp = 1'b0;

red_tmp = ~red_tmp;

HEX_1 = 7'b000_0110; // E

HEX_2 = 7'b000_0110; // E

end

RIGHT_PASS: begin

green_tmp = ~green_tmp;

red_tmp = 1'b0;

HEX_1 = 7'b000_0010; // 6

HEX_2 = 7'b100_0000; // 0

end

STOP: begin

green_tmp = 1'b0;

red_tmp = ~red_tmp;

HEX_1 = 7'b001_0010; // 5

HEX_2 = 7'b000_1100; // P

end

endcase

end

assign RED_LED = red_tmp ;

assign GREEN_LED = green_tmp;

endmodule

©版权声明:本文内容由互联网用户自发贡献,版权归原创作者所有,本站不拥有所有权,也不承担相关法律责任。如果您发现本站中有涉嫌抄袭的内容,欢迎发送邮件至: www_apollocode_net@163.com 进行举报,并提供相关证据,一经查实,本站将立刻删除涉嫌侵权内容。

转载请注明出处: apollocode » 停车场系统的Verilog代码

文件列表(部分)

| 名称 | 大小 | 修改日期 |

|---|---|---|

| 停车场系统的Verilog代码.txt | 1.19 KB | 2020-03-29 |

| p1.png | 39.71 KB | 2020-03-29 |

| image | 0.00 KB | 2020-03-29 |

发表评论 取消回复