算术逻辑单元(ALU)的VHDL代码

应用介绍

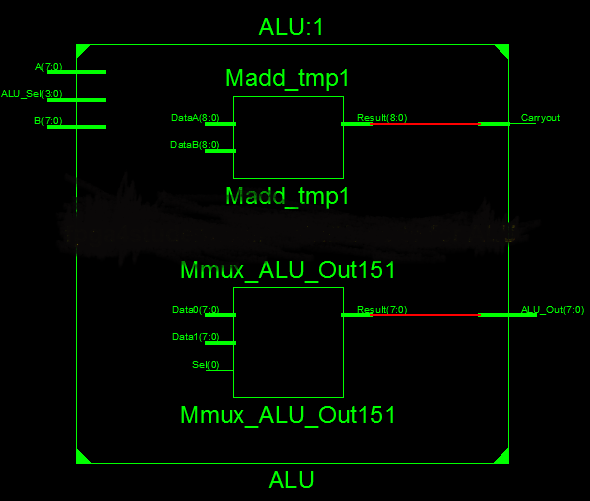

此项目是算术逻辑单元(ALU)的VHDL代码。

算术逻辑单元(ALU)是CPU中最重要的数字逻辑组件之一。 它通常执行逻辑和算术运算,例如加法,减法,乘法,除法等。

在VHDL中设计并实现了ALU。 完整介绍了ALU的VHDL代码。

ALU中实现的逻辑和算术运算如下:

1.算术加法

ALU_Out = A + B;

2.算术减法

ALU_Out = A-B;

3.算术乘法

ALU_Out = A * B;

4.算术除法

ALU_Out = A / B;

5.逻辑左移

ALU_Out =逻辑左移1;

6.逻辑右移

ALU_Out =逻辑右移1;

7.向左旋转

ALU_Out =向左旋转1;

8.向右旋转

ALU_Out =向右旋转1;

9.逻辑与

ALU_Out = A和B;

10.逻辑或

ALU_Out = A或B;

11.逻辑异或

ALU_Out = A XOR B;

12.逻辑或非

ALU_Out = A NOR B;

13.逻辑与非

ALU_Out = A NAND B;

14.逻辑XNOR

ALU_Out = A XNOR B;

15.大的比较

如果A> B,则ALU_Out = 1否则为0;

16.平等比较

ALU_Out = 1 A = B否则为0;

附件中包括:ALU的VHDL代码、ALU的Testbench VHDL代码。

本人在下方展示了ALU的VHDL代码;想了解更多请下载附件。

-- fpga4student.com: FPGA Projects, Verilog projects, VHDL projects

-- VHDL code for ALU

-- @fpga4student

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

use ieee.NUMERIC_STD.all;

-----------------------------------------------

---------- ALU 8-bit VHDL ---------------------

-----------------------------------------------

entity ALU is

generic (

constant N: natural := 1 -- number of shited or rotated bits

);

Port (

A, B : in STD_LOGIC_VECTOR(7 downto 0); -- 2 inputs 8-bit

ALU_Sel : in STD_LOGIC_VECTOR(3 downto 0); -- 1 input 4-bit for selecting function

ALU_Out : out STD_LOGIC_VECTOR(7 downto 0); -- 1 output 8-bit

Carryout : out std_logic -- Carryout flag

);

end ALU;

architecture Behavioral of ALU is

signal ALU_Result : std_logic_vector (7 downto 0);

signal tmp: std_logic_vector (8 downto 0);

begin

process(A,B,ALU_Sel)

begin

case(ALU_Sel) is

when "0000" => -- Addition

ALU_Result <= A + B ;

when "0001" => -- Subtraction

ALU_Result <= A - B ;

when "0010" => -- Multiplication

ALU_Result <= std_logic_vector(to_unsigned((to_integer(unsigned(A)) * to_integer(unsigned(B))),8)) ;

when "0011" => -- Division

ALU_Result <= std_logic_vector(to_unsigned(to_integer(unsigned(A)) / to_integer(unsigned(B)),8)) ;

when "0100" => -- Logical shift left

ALU_Result <= std_logic_vector(unsigned(A) sll N);

when "0101" => -- Logical shift right

ALU_Result <= std_logic_vector(unsigned(A) srl N);

when "0110" => -- Rotate left

ALU_Result <= std_logic_vector(unsigned(A) rol N);

when "0111" => -- Rotate right

ALU_Result <= std_logic_vector(unsigned(A) ror N);

when "1000" => -- Logical and

ALU_Result <= A and B;

when "1001" => -- Logical or

ALU_Result <= A or B;

when "1010" => -- Logical xor

ALU_Result <= A xor B;

when "1011" => -- Logical nor

ALU_Result <= A nor B;

when "1100" => -- Logical nand

ALU_Result <= A nand B;

when "1101" => -- Logical xnor

ALU_Result <= A xnor B;

when "1110" => -- Greater comparison

if(A>B) then

ALU_Result <= x"01" ;

else

ALU_Result <= x"00" ;

end if;

when "1111" => -- Equal comparison

if(A=B) then

ALU_Result <= x"01" ;

else

ALU_Result <= x"00" ;

end if;

when others => ALU_Result <= A + B ;

end case;

end process;

ALU_Out <= ALU_Result; -- ALU out

tmp <= ('0' & A) + ('0' & B);

Carryout <= tmp(8); -- Carryout flag

end Behavioral;

©版权声明:本文内容由互联网用户自发贡献,版权归原创作者所有,本站不拥有所有权,也不承担相关法律责任。如果您发现本站中有涉嫌抄袭的内容,欢迎发送邮件至: www_apollocode_net@163.com 进行举报,并提供相关证据,一经查实,本站将立刻删除涉嫌侵权内容。

转载请注明出处: apollocode » 算术逻辑单元(ALU)的VHDL代码

文件列表(部分)

| 名称 | 大小 | 修改日期 |

|---|---|---|

| 算术逻辑单元(ALU)的VHDL代码 (附件).txt | 1.35 KB | 2020-04-05 |

| aLU1.png | 30.01 KB | 2020-04-05 |

| image1 | 0.00 KB | 2020-04-05 |

发表评论 取消回复